ニュース

車載ミリ波レーダーの低コスト化を実現するCMOS送受信チップの試作に成功【富士通研究所】

2014年10月8日

㈱富士通研究所(注1)は、低コスト化が可能な半導体プロセスであるCMOSを使用したミリ波レーダー用送受信チップを試作し、近距離検知性能向上を実現することに成功しました。

従来ミリ波レーダーには、SiGe(シリコンゲルマニウム)送受信チップが使われていますが、SiGeより低消費電力で低コスト化が図りやすいCMOSでは、特に低周波領域でのノイズ低減が課題となり、ミリ波レーダーとして実用的なものを作ることは困難でした。

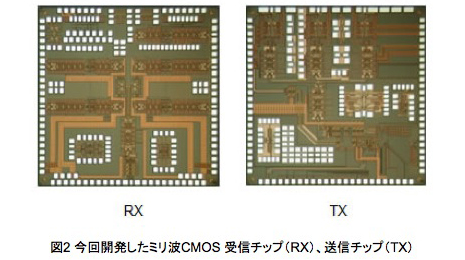

今回、車載ミリ波レーダーで使用される76-81GHz(ギガヘルツ)に対応可能な周波数変換回路の構成を工夫することで、受信回路における発振器のノイズ を抑制したCMOS送受信チップの試作に成功しました。従来のCMOSを使用した研究結果に比べてノイズを大幅に低減でき、既存のSiGeチップと同等以 上の性能が得られています。

本技術を使うことで、SiGeに比べ消費電力が約半分で、低コストを実現するCMOSチップでのミリ波レーダーを実現できます。

本技術の詳細は、10月5日(日曜日)からイタリア・ローマで開催される国際会議「EuMC 2014(European Microwave Conference 2014)」で発表します。

開発の背景

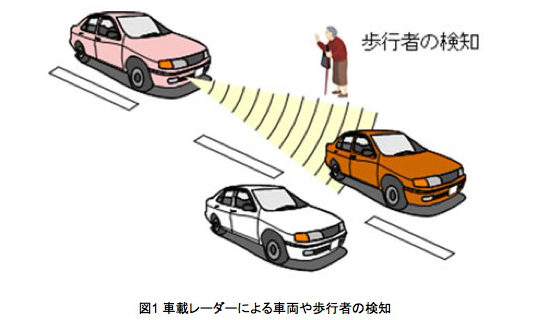

自動車を安全で快適に運転するために、車の周辺の障害物を検知し、その状況に応じてブレーキやアクセルを制御する技術が急速に普及しつつあります。障害物を検知するセンサーとしては、ミリ波レーダーやレーザーレーダー、ステレオカメラなどがあります。特にミリ波レーダーは、レーザーレーダーやステレオカメラの可視光線を使うセンサーに比べて雨、霧や逆光などの影響を受けにくい特長があり、車載用のセンサーとして重要な役割をはたしています。今後こうしたセンサーを自動車に搭載するに当たり、センサー自体を低コストに実現する技術が求められていました。

課題

ミリ波レーダーは、使用する電波が76-81GHzという非常に高い周波数であるミリ波を使っているため、従来はSiGeバイポーラトランジスタなどの特殊な半導体を使う必要がありました。しかし半導体技術の進歩によって、デジタル回路で一般的に使用されていて、かつ低コスト化が可能なCMOSでも、ミリ波回路の実現が可能になってきました。CMOSは従来のSiGeバイポーラトランジスタに比べて低い電源電圧で動作可能なため消費電力を小さくでき、ミリ波領域(76-81GHz)において概ね同等の性能を示すものの、低周波領域でのノイズ成分が大きいという問題がありました。

ミリ波レーダーの場合、発振器のミリ波信号を送信し、障害物で反射してきた信号と元の送信信号との差分を比較することで、障害物の距離・速度・方位の検出を行います。特に近い距離にある反射の弱い歩行者などの検知性能を向上させるには、この低周波領域のノイズの低減が求められていました。

開発した技術

ミリ波レーダーでCMOSを使う場合、近距離の検知性能を確保するには低周波領域のノイズ成分を低減する工夫が必要です。

今回の開発した技術の特長は以下のとおりです。

1. 受信チップの高周波特性を確保すると同時に低周波領域のノイズを低減。

2. 従来のSiGeバイポーラトランジスタを使ったものに比べ、消費電力1/2を実現。

今回、受信回路の中の周波数変換回路にダブルバランスト・レジスティブ・ミキサを採用しました。周波数変換回路は、送信信号と同一の局部発振信号(LO信号)と障害物で反射して戻ってきた信号(RF信号)との周波数差分の信号(IF信号)を取り出す働きをしています。レジスティブ・ミキサはミキサのトランジスタに電源電圧を印加せずLO信号の電力によってIF信号を取り出す回路形式です。電源電圧を印加しないので、ミキサのトランジスタに流れるDC電流の発生を最小限に抑えることができ、このことで低周波領域でのノイズ上昇を防ぐことが可能です。さらに、レジスティブ・ミキサを差動合成するダブルバランス構成にすることで、ミキサに入力するLO信号の電力によって発生するDCオフセットによるノイズ上昇も抑えることができ、10kHz以下のノイズ低減と高周波特性の両立に成功しました。

この回路を使用して、現行のSiGe製品と同等の機能を有した4chの受信チップを試作しました。また昨年発表した低位相ノイズのPLLシンセサイザを採用した送信チップも併せて試作し、ミリ波レーダーを構成する主要な高周波半導体回路全体を一般的な65nm(ナノメートル) CMOSプロセスで実現することに成功しました(図2)。受信チップの低周波領域のノイズを表すSSBノイズ指数で比較すると、本発表のものは12dBであり、従来のSiGe製品と同等以上で、従来学会などで発表されていたCMOSの30dBに対しては18dB改善しています。この改善はノイズの大きさが約60分の1と大幅に低減したことに相当します(注2)。

従来のSiGeは電源電圧が3~5Vで動作するのに対し、今回のCMOSは1.2Vの電源電圧で同等の性能を実現しており、消費電力を半分程度にすることにも成功しています。

効果

今回実現した低周波領域のノイズ低減によって、ミリ波レーダーの近距離域の検知性能が向上するため、レーダー波の反射が弱く近距離での検知が必要な歩行者などの検知性能向上に貢献します。

本技術はデジタル回路で一般的に使用している65nm CMOSプロセスを使用しているため、大量生産が可能で低コスト化も容易です。またCMOSチップで消費する電力も従来のSiGeバイポーラトランジスタを使ったものに比べ約半分になるため、レーダーセンサーの電源回路も含めた回路の低コスト化が可能になります。さらに、デジタル回路の混載も容易で今後のミリ波レーダーの高機能化にも対応可能です。

今後

2018年頃の実用化を目指すとともに、ミリ波レーダーの高機能化も進めていく予定です。

商標について

記載されている製品名などの固有名詞は、各社の商標または登録商標です。

【注釈】

注1 ㈱富士通研究所 :

代表取締役社長 佐相秀幸、本社 神奈川県川崎市。

注2 約60分の1の低減 :

X dBは10^(X/10) [10の(X/10)乗]で表すため、18dBのノイズ改善は10^(18/10)の逆数、すなわち約60分の1となる。

【本件に関するお問い合わせ】

㈱富士通研究所

ネットワークシステム研究所 先端ワイヤレス研究部

電話 044-754-2647(直通)

メール mm-wave@ml.labs.fujitsu.com

プレスリリースに記載された製品の価格、仕様、サービス内容、お問い合わせ先などは、発表日現在のものです。その後予告なしに変更されることがあります。あらかじめご了承ください。

株式会社富士通研究所ホームページはこちら