ニュース

次世代パワーデバイスの理想性能に近づく絶縁膜材料作製手法を開発【科学技術振興機構】

2014年7月25日

~SiCと絶縁膜の界面欠陥解消による性能向上へ~

ポイント

○パワーデバイスによる大幅な省エネは、材料由来の欠陥によって足踏みしている。

○原因は材料生成時の熱処理における炭素残留であり、残留させない反応条件を見いだした。

○結果、材料欠陥が世界最小値まで減少し、理想的な材料性能を発揮できることを確認。

○この技術により、SiCパワーデバイスの高性能化と普及の促進が期待できる。

JST 戦略的創造研究推進事業において、東京大学 大学院工学系研究科の喜多 浩之 准教授らは次世代のパワーデバイス注1)材料として期待されるシリコンカーバイド(SiC)注2)上に形成される絶縁膜材料との間の「界面欠陥注3)」を大幅に低減し、理想性能に近づける新しい改質手法を開発しました。

エネルギー利用の高効率化への期待が高まる中、その「切り札」の1つが次世代パワーデバイスであり、変圧器やインバータとして電力システム、電気自動車、工場設備をはじめとする多くの用途で電力損失を大きく低減できると期待されています。また、従来の半導体材料(シリコン)を用いたパワーデバイスによる電力の利用効率は限界に近づいていますが、SiCは、大幅な低電力損失での制御・動作が可能であり、加えて機器の小型化、低コスト化、高電圧機器への適用が実現できるなど、次世代パワーデバイスの理想的な材料として期待されています。

しかし、理想的な材料であるSiCを用いてパワーデバイスの構成素子であるトランジスターを作成しても、現状では電気抵抗が大きい、動作信頼性が低いなどの課題が生じており、原因であるSiCと、その表面に形成されるゲート絶縁膜注4)材料(二酸化ケイ素・SiO2)との間の「界面欠陥」を減らすことが求められていました。

本研究者らは、ゲート絶縁膜を形成する際に欠陥を生じるSiC由来の副生炭素を一酸化炭素(CO、気体)として排出する反応条件を用いることで、界面欠陥を大幅に低減できることを発見しました。そしてデバイス素子のモデル構造を試作し、界面状況を観察した結果、欠陥(界面欠陥準位密度注5))が世界最小値(1011cm-2eV-1以下)へ低減できることを実証しました。

本手法は、窒素系ガスを添加するなどの付加的プロセスなしに、極めて高い品質の界面を実現したものであり、各種産業における利用が期待される手法と考えられます。本手法により、長期安定性も含めたSiCパワーデバイスの性能向上と普及が可能となり「エネルギーの高効率利用」への貢献が期待できます。

本研究成果は、米国物理学協会発行の応用物理学誌「Applied Physics Letters」のオンライン版で近く公開されます。

本成果は、以下の事業・研究領域・研究課題によって得られました。

戦略的創造研究推進事業 個人型研究(さきがけ)

研究領域 「エネルギー高効率利用と相界面」

研究総括 笠木 伸英 JST研究開発戦略センター 副センター長・上席フェロー、東京大学 名誉教授

研究課題名 「SiC MOSFETの抵抗損失低減のための界面制御技術」

研究代表者 喜多 浩之(東京大学 大学院工学系研究科 准教授)

研究期間 平成23年12月~平成27年3月

<研究の背景と経緯>

昨今、新エネルギーあるいは蓄エネルギーへの期待と開発機運が世界中で高まっていますが、省エネルギーにもまだまだ多くの改善の余地が残されています。 その「省エネの切り札」が次世代のパワーデバイスであり、電力送電の変圧や工場生産設備、電気自動車のモーターやエアコン、太陽光発電、照明器具など、多くの用途で大幅な電力の高効率利用が求められ、実現できる材料の探究が、日本はもとより米国、欧州といった諸外国においても活発に進められています。

この電力の高効率利用は、このような高電圧や周波数の変換、大電流の直流と交流の変換などを行うパワーデバイスの動作時の電力損失低減によって初めて実現されます。

パワーデバイスには従来、半導体材料であるシリコンを用いていましたが、材料由来の電力利用特性は限界にきており、次世代材料の1つであるシリコンカーバイド(SiC)の高い電子移動度、高い絶縁破壊電界強度という特性が、動作時の抵抗損失を数百分の一まで低減できると期待されています。

しかし、パワーデバイスを構成する素子であるSiCトランジスターの現状は、ゲート絶縁膜とSiCの界面に形成される反転層チャネル注6)中の電子移動度注7)は多くの場合、数10cm2V-1s-1程度と小さく、期待される性能を発揮することができません。その原因は、ゲート絶縁膜である二酸化ケイ素(SiO2)を形成するためにSiCを熱酸化反応する際、副生成物である炭素を取り込みながらSiO2が成長してしまい、それが界面欠陥となるからです。この界面欠陥が高密度に存在することにより、電子の移動を妨げ、結果としてトランジスターの抵抗損失が増大し、さらに閾(しきい)電圧注8)の経時変化によって動作不良を生じるなど、SiCパワーデバイスの普及の大きな障害となっていました。

<研究の内容>

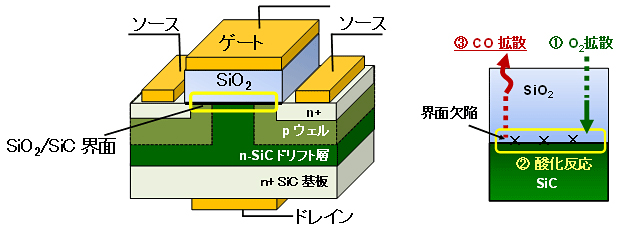

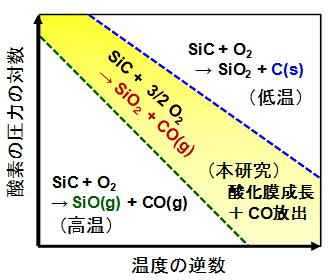

SiCとSiO2の界面の欠陥密度の低減には、SiCの熱酸化反応の副生成物として発生する炭素を、SiO2の形成と同時に系外へ排出する手法(図1)などを用いることで界面欠陥を低減することが必要となります。SiCの熱酸化には種々の反応様式があり、反応温度や酸素の供給圧力によって主要な反応が変化します(図2)。

副生成物である炭素が固体元素で存在する場合には、界面やSiO2中にとどまりやすいのですが、気体分子の一酸化炭素(CO)に変化させればSiO2膜中を速やかに透過して外気へと速やかに除去することができます。

そこで本研究者らはSiCの熱酸化の条件を制御し、SiO2とCOが同時に生成する反応が支配的となる条件だけを選択的に使用することで、熱酸化反応で生じる炭素を気体状のCOとして系外に排出することができると予想しました。

このような条件を満たす反応は、例えば六方晶結晶である4H-SiCの代表的な結晶面(0001面)の場合、1気圧の酸素雰囲気中では1,300℃前後で実現されることが、実験的にも、熱力学計算からも示唆されました。しかし、実用されているような通常の加熱装置を用いた熱酸化反応操作では、反応終了後の冷却過程で低温での酸化反応が生じ、炭素を副生してしまいます。また、冷却時の低温酸化反応を防ぐために、冷却時に酸素を遮断しても酸素分圧が低下し、理想条件から外れてしまうなど適切な反応条件とするには温度調節も重要な要件であることが明らかになりました(図2)。そこで本研究者らは急速な温度調節が可能なランプ加熱炉注9)を用い、高温の理想的な酸化条件だけを選択的に利用できる手法を開発し、実証実験を行いました。

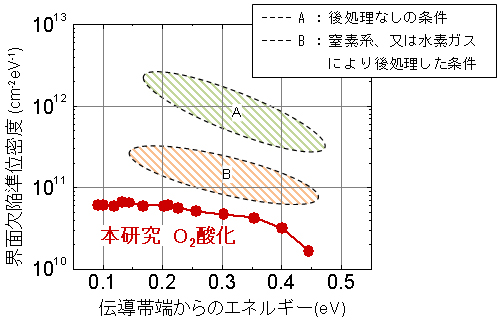

本研究者らは実証実験の結果として、界面近傍の欠陥の存在状態を検討するためにデバイスのモデル素子構造としてMOS(金属―酸化物―半導体)キャパシター注10)を形成して、界面の欠陥密度の指標となる界面欠陥準位密度(Dit)を評価したところ、SiCの伝導帯端から0.1eV~0.5eVの範囲で1010~1011cm-2eV-1の範囲にあり、界面欠陥が大きく減少しているという結果が得られました。

この値は、4H-SiCで従来用いられていた熱酸化(乾燥条件)では1012cm-2eV-1以上の値が報告されており、熱酸化反応後にさらに一酸化窒素や水素による処理を加えた場合でも1011cm-2eV-1程度であったのに比べて小さな値であり、4H-SiCのDitとしては世界最小レベルの値です(図3)。特に伝導帯エネルギーに近いエネルギーレベルの界面欠陥準位密度が大幅に低下していることから、トランジスターの反転層チャネル中の電子移動度が大きくなることが予想されます。また、MOSキャパシターの加える電圧に対する電気容量の変化の仕方は静電場に関するポアソン方程式注11)から導かれる理論的な予測とほぼ一致していることからも界面欠陥密度が大幅に低下し、理想的な材料特性が発揮できたことが示されています。

これまでは界面欠陥の影響を除くために熱酸化反応後に一酸化窒素などによる処理が広く行われていましたが、本研究はこれらの添加物による後処理を行うことなく、熱酸化条件を工夫するという非常に基本的な酸化技術だけで、後処理を行う場合以上に界面欠陥を低減できることを示しています。

<今後の展開>

現在までに実用化、または開発中のSiCトランジスター(MOSFET、IGBT)の製造プロセスのゲート絶縁膜形成の工程を本手法に置き換えることで、界面欠陥が減少します。その結果、MOS反転層チャネル中の電子移動度の向上によってSiCパワートランジスターの抵抗損失の低減が期待できます。また、この界面欠陥の減少によって、動作時の閾電圧の変動も小さくなるため、デバイスの信頼性が向上し、より多くの用途へ普及することが期待できます。

なお、本研究は六方晶結晶である4H-SiCの代表的な結晶面(0001面)に対する効果を実証しましたが、条件を調整することで他の結晶面の熱酸化にも応用できるため、次世代のトランジスターとして期待されるトレンチ型MOSFET注12)などのデバイス構造においても有効な手法となることも期待されます。

<参考図>

図1 SiCトランジスタ(左)および熱酸化により形成するSiO2/SiC界面(右)の模式図

図1 SiCトランジスタ(左)および熱酸化により形成するSiO2/SiC界面(右)の模式図

SiCの熱酸化は、①酸素の拡散(流入)、②酸化反応(界面でのSiO2形成)、③副生成物の炭素の放出(CO拡散)の3段階で進行する。炭素のCOとして除去される過程を促進すれば、理想的なSiO2/SiC界面構造の形成が阻害されず、界面欠陥の低減が期待される。

図2 SiCの熱酸化の主要な反応様式が、温度と圧力によって変化するイメージ図

図2 SiCの熱酸化の主要な反応様式が、温度と圧力によって変化するイメージ図

横軸が温度変化(逆数なので左部が高温領域)、縦軸が酸素量変化(分圧。上部ほど酸素量が多い領域)の条件分布を表す。

このうち、SiO2が生成し、かつCが元素状炭素でなく気体分子状のCOとなる反応が支配的となる範囲(図中の点線囲いで黄塗部分)を選択的に利用すればCOとして炭素の除去が促進されるはずだと考えた。

図3 本研究で得られたSiO2/4H-SiC界面の欠陥準位密度を従来の値と比較した

横軸には、界面欠陥準位のエネルギーをSiCの伝導帯エネルギー端を基準にとって示した。従来の4H-SiCについての典型的な値よりも低減されており、特にNOやH2の処理を施した例よりもさらに低い値が得られる。また、伝導帯端に近いエネルギー領域(0.1eV~0.2eV)において世界で初めて<1011cm-2eV-1を実現した。

<用語解説>

注1)パワーデバイス

大電流・高電圧あるいは、高周波数を用いる電力機器向けの半導体素子の総称であり、中心部品。電圧・電流・周波数を変換・制御するなどの電力制御用に最適化され、家庭用電化製品、コンピューターから電気自動車、送電システムなど幅広く用いられる。

注2)シリコンカーバイド(SiC)

炭化ケイ素。ケイ素(Si)と炭素(C)からなる半導体物質。現在利用されている半導体材料はSiであるが動作速度、電圧、電流、冷却系などで、ほぼ限界に近くなってきている。他方、SiCは、SiとCと結びつくことで次世代のパワーデバイスに必要な低電流抵抗、高電圧耐圧、高耐熱などさまざまな性能を持つ材料であり、「省エネの切り札」と期待されている。 電力を効率よく制御するために、電流容量が大きい(オン抵抗が低い)、耐電圧が大きい、発熱が少なく放熱が良いパワーデバイスが望まれる。

注3)界面欠陥

一般に、「欠陥」とは結晶構造のなかで、不純物などの混入によって、その構造が乱れている状態を示す。ここでは、SiCトランジスターでスイッチの役割をするゲート絶縁膜SiO2と、SiCの界面近傍に存在する不純物、構造の乱れなどにより生じる欠陥を表す。

注4)ゲート絶縁膜

電界効果型トランジスターにおいて、通電部分であるチャネルと、チャネルの通電状態を切り替える電圧を入力するゲート電極との間を、電気的に絶縁する膜のこと。

注5)界面欠陥準位密度

界面欠陥により生じるエネルギー準位の密度を表す。ただし、本稿では、SiCの伝導帯端からエネルギー準位の変異ごとの存在密度として表す。

注6)反転層チャネル

電界効果型トランジスターにおいて、ゲート絶縁膜と接する半導体表面に形成される、電子やホールの通り道のこと。ゲート電極に入力する信号によって通電状態と切断された状態が変化する。

注7)電子移動度

加えた電界によって電子やホールが運ばれる時、その速度の指標となる物性値のこと。

注8)閾(しきい)電圧

電界効果型トランジスターにおいて通電状態と切断状態を切り替えるために必要なゲート電圧の大きさのこと。

注9)ランプ加熱炉

赤外線加熱方式により、急速な加熱、および冷却が可能な電気炉。従来の半導体材料であるシリコンを使った製造プロセスでも利用される加熱・冷却装置のこと。

注10)キャパシター

誘電体を2つの導体または半導体で挟んだ構造を持ち、加える電圧の変化によって電荷を蓄積・放出する素子。

特に金属―酸化物―半導体で構成したものをMOSキャパシターと呼ぶ。

注11)静電場に関するポアソン方程式

静電ポテンシャルと電荷分布の関係を表す微分方程式のこと。

注12)トレンチ型MOSFET

半導体チップ表面に溝(トレンチ)を作り、その側面にゲート構造を配置した形のトランジスター。内部の抵抗が小さく出来ることから、次世代のSiCパワーデバイスとして開発されている。

<論文タイトル>

“Fabrication of SiO2/4H-SiC (0001) Interface with Nearly-Ideal Capacitance-Voltage Characteristics by Thermal Oxidation”

(理想的な電気容量―電圧を示すSiO2/4H-SiC(0001)界面の熱酸化による形成)

doi : 10.1063/1.4891166

<お問い合わせ先>

<研究に関すること>

東京大学 大学院工学系研究科 マテリアル工学専攻 准教授

〒113-8656 東京都文京区本郷7-3-1

Tel : 03-5841-7164 Fax : 03-5841-7164

E-mail : kita@scio.t.u-tokyo.ac.jp

<JST事業に関すること>

科学技術振興機構 戦略研究推進部 グリーンイノベーション・グループ

〒102-0076 東京都千代田区五番町7 K’s五番町

Tel : 03-3512-3525 Fax : 03-3222-2066

E-mail : presto@jst.go.jp

<報道担当>

科学技術振興機構 広報課

〒102-8666 東京都千代田区四番町5番地3

Tel : 03-5214-8404 Fax : 03-5214-8432

東京大学 大学院工学系研究科 広報室

〒113-8656 東京都文京区本郷7-3-1

Tel : 03-5841-1790 Fax : 03-5841-0529

独立行政法人科学技術振興機構ホームページはこちら