ニュース

欠陥密度を大幅低減したパワー半導体用SiCエピウェハーを販売【昭和電工】

2015年10月2日

昭和電工㈱(社長:市川 秀夫)は、パワー半導体の材料である炭化ケイ素(以下、SiC)エピタキシャルウェハー(以下、エピウェハー)の4インチ(100mm)品と6インチ(150mm)品において、欠陥を大幅に低減した新グレード「ハイグレードエピ(以下、HGE)」を開発し、今月より販売を開始いたします。

SiCパワー半導体は、現在主流のシリコン製に比べ耐高温・高電圧特性や、大電流特性に優れ、電力損失も大幅に削減できることから、電力制御に用いるモジュールの軽量・小型化と高効率化を実現する次世代型パワー半導体として注目されています。すでにデータセンターのサーバー電源や新エネルギーの分散型電源、地下鉄車両に採用が進んでいますが、自動車への搭載も表明され、今後さらなる需要拡大が期待されています。また、発電・送電系統への適用を目的とした10KV級超高耐圧デバイスの研究開発も進められています。

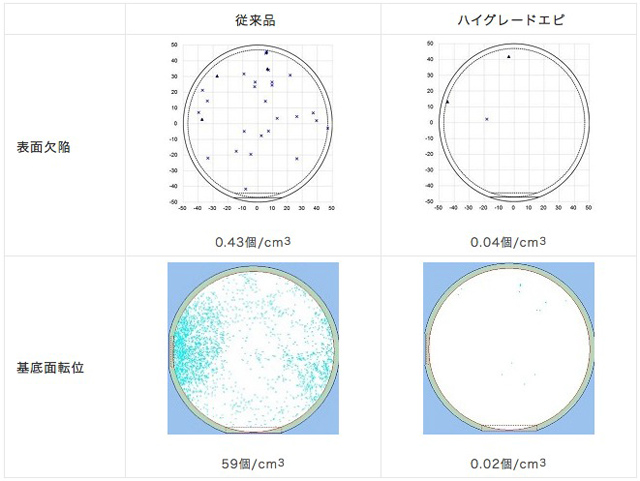

高電圧・大電流に耐えうるパワーモジュールには主にSBD*とMOSFET**が搭載されており、現在、SBDにおいてSiCの採用が進んでいます。一方、MOSFETはエピウェハー表面に形成する酸化膜をデバイス動作に用いることから、SBDに比べ微細な表面欠陥や、基底面転位***をはじめとする結晶欠陥がデバイスの収率(歩留まり)や品質に大きく影響し、SiC-MOSFETの実用化には、欠陥の低減が課題となっていました。

また自動車向けのモジュールなどは、100A級の大電流を一つのデバイスで扱うため、エピウェハーから生産されるSiCチップが10mm角級に大型化されます。このような大型チップでは、生産時の収率(歩留まり)悪化を防ぐため、エピウェハーの欠陥密度を0.1個/cm2以下に抑える必要があります。

今回開発したHGEでは、表面欠陥を当社従来品の3分の1である0.1個/cm2に、基底面転位を従来品の100分の1以下である0.1個/cm2以下にコントロールすることが可能となりました。代表的な結晶欠陥である基底面転位によるデバイス不良の割合がほぼ0になることから****、HGEは、SiC-SBDとSiC-MOSFETの組合せにより作成されるフルSiCパワーモジュールの実用化と市場拡大に大きく寄与すると考えています。

加えて、同技術の適用により、発電・送電系統向け超高耐圧デバイス用として必要とされる100μm*****以上の膜厚を有するエピウェハーにおいても、低レベルの欠陥密度と良好な均一性の確保が可能となることから、HGE製品として出荷を開始いたします。

SiCパワー半導体エピタキシャルウェハーの市場規模は、2025年に1,000億円規模に拡大すると予想されています。当社は今後も市場の要求品質に応え、市場形成に貢献してまいります。

* SBD(Schottky Barrier Diode)…ショットキーバリアダイオード

** MOSFET(Metal Oxide Semiconductor Field Effect Transistor)

金属酸化膜半導体電界効果トランジスタ

*** 基底面転位…SiC単結晶の基底面に発生する転位

**** 10mm角チップでの想定

***** 1μm(マイクロメートル)=1000分の1mm

昭和電工株式会社ホームページはこちら