ニュース

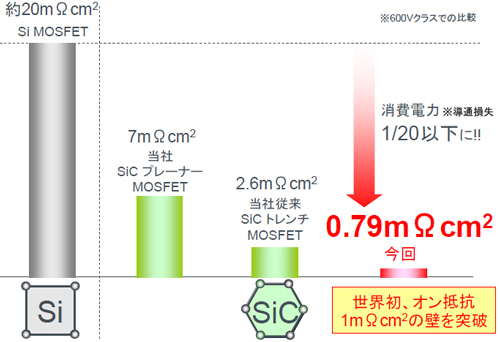

世界で初めてオン抵抗1mΩ・cm2の壁を破る※1 超低損失SiCトレンチMOSFETを開発【ローム】

2011年12月5日

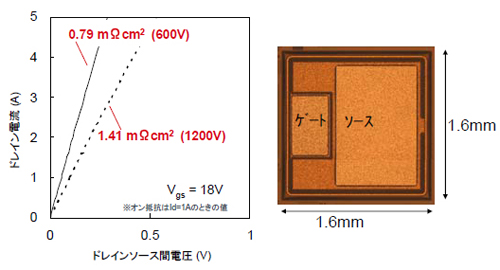

半導体メーカーのローム㈱(本社:京都市)は、このほど、超低損失SiCトレンチMOSFETを開発しました。600Vでは0.79mΩ・cm2 、1200Vでは 1.41mΩ・cm2という※1世界最小の超低オン抵抗を実現しており、1mΩ・cm2以下のオン抵抗を実現したのは世界初の快挙となります。

今回の開発成果は、従来のSi-MOSFETに比べて1/20以下、量産化されているSiCデバイスに比べても1/7以下のオン抵抗となり、電力送電網の電力変換から、パソコンやデジタル家電の電源、冷蔵庫やエアコンのインバータ、電気自動車、鉄道車両に至るまで、身の回りのあらゆる所の電力変換器で発生している電力損失を1/20以下にまで大幅低減するものとして期待できます。

エネルギー問題、地球環境問題の解決にも大きく貢献するデバイスとして、ロームでは既にSiC-SBDやSiC-DMOSFETなどを量産していますが、更なる低損失化を実現すべく2013年度中を目途にSiCトレンチMOSFETの実用化を進めてまいります。

なお、本成果は、12月5日~7日に米国ワシントンDCで開催されるIEDM(International Electron Devices Meeting:国際電子デバイス会議)において発表する予定です。

東日本大震災以降、電力問題が大きく取り沙汰されています。また、BRICSを中心とする新興国においては、エネルギー消費量が今後急増するという予測が出ており、世界規模でのエネルギー問題への対応も叫ばれています。

これらの解決策として再生可能エネルギーや省エネ製品などに注目が集まっていますが、エネルギーを効率的に輸送する技術(高効率化・低損失化技術)も非常に重要な役割を果たします。

一般的に電力を発電してから各種機器で消費するまでの間には、電流を交流から直流に変えたり、電圧を上げ下げしたりと数多くの電力変換が繰り返されます。この間、多い場合で実に50%もの電力が失われているといわれているのです。

こうした電力損失を劇的に減らすキーデバイスとして期待されているのがSiCパワーデバイスです。従来のSi半導体を全てSiCに置き換えた場合の省エネ効果は日本国内だけで原発4基分※2に相当するとの試算も出ています。ロームでは、こうした流れを先取りし、2010年に世界で初めてSiC-DMOSFETの量産に成功するなど、業界をリードする開発を進めてまいりました。

※1 : ローム調べ(2011年12月4日現在)

※2 : エンジニアリング振興協会調べ : 2020年時点で日本国内主要分野でSiCパワーデバイスが導入された場合(100万kW級原発1基=8.8TWh/年として試算)

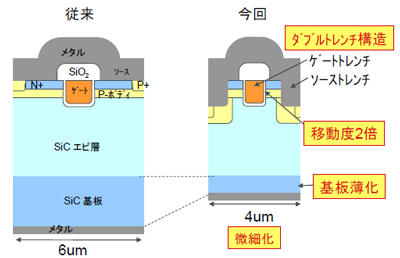

今回は、基板薄化と微細化、チャネル移動度の向上に加え、独自のダブルトレンチ構造の採用により超低オン抵抗と高耐圧の両立に成功しました。ロームでは、これまでもトレンチ構造を採用したSiCトレンチMOSFETの開発に成功しておりましたが、SiCに期待されるオン抵抗値に対して依然として改善の余地がありました。

そこで、基板の厚さを従来の350umから100umまで薄化することにより基板抵抗を約70%低減し、さらに微細化とチャネル移動度を2倍に向上することによりチャネル抵抗を約80%低減することに成功し、大幅な低オン抵抗化を達成しました。

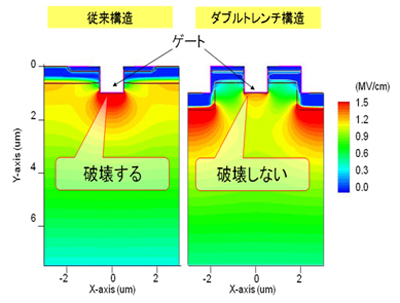

また、ゲートとソースにトレンチを形成する独自の電界緩和構造であるダブルトレンチ構造で、トレンチ構造の弱点である高電圧時のトレンチ底部ゲート酸化膜破壊を克服することにも成功しました。

今回の技術の応用により、例えば電気自動車の場合、インバータ部分の小型化はもちろん、周辺部品の小型化や冷却機構の簡素化なども図れるため、航続距離の大幅改善が実現できます。また、パソコンから電力送電網に至るまで、あらゆる機器において、電力変換時の損失低減が期待できるため、エネルギー問題、地球環境問題という観点からも世界に大きく貢献できると考えられます。

ロームでは、SiC デバイス事業を次世代半導体事業の中核技術の一つとして位置付けており、DMOSFET やSBD のさらなる高耐圧化、大電流化製品のラインアップの強化のほか、SiC トレンチMOSFET やSiC デバイスを搭載したIPM(インテリジェント・パワー・モジュール)などSiC 関連製品のラインアップ拡充、量産化を進めてまいります。

なお、今回の成果の一部は、京都大学大学院 工学研究科 木本 恒暢 教授との共同研究によるものです。

オン抵抗を70%削減 ※当社従来SiCトレンチMOSFET 比

今回の特性波形と素子外観

基板薄化に加え、微細化に成功し、超低オン抵抗を実現

ダブルトレンチ構造の電界分布

ゲート部分の電界が高いと壊れやすい(ゲート部が赤いほど壊れやすい)

用語説明

1. IEDM(International Electron Devices Meeting:国際電子デバイス会議)

最先端デバイス研究の発表の場として歴史も古く、世界的に権威の高い国際会議のひとつ。

2. オン抵抗

パワー素子の動作時(通電時)の抵抗値。パワーMOSFETの性能を左右する最も重要なパラメータで、値が小さいほど電力損失が少なくなる。

3. MOSFET(Metal-Oxide-Semiconductor Field Effect Transistorの略)

金属-酸化物-半導体電界効果トランジスタのことで、FETの中では最も一般的に使用されている構造である。スイッチング素子として使われる。

4. SBD(ショットキー バリア ダイオード Schottoky Barrier Diodeの略)

金属と半導体を接触させることでショットキー接合が形成され、整流性(ダイオード特性)が得られることを利用したダイオード。少数キャリア蓄積効果が無く高速性に優れているという特徴を持つ。

5. トレンチ型構造

トレンチは溝を意味する。チップ表面に溝を形成し、その側壁にMOSFETのゲートを形成した構造。プレーナー型MOSFETに構造上存在するJFET抵抗が存在せず、プレーナー構造よりも微細化が可能なため、SiC材料本来の性能に近いオン抵抗が期待できる。

ローム株式会社ホームページはこちら