ニュース

一世代先行する16nm UltraScale+ ファミリを発表、最新のメモリ、3D-on-3D、マルチプロセッシングSoC技術を採用【ザイリンクス】

2015年2月24日

新しいUltraScale+ FPGA、SoC、3D ICデバイスが、LTE Advancedおよび5Gワイヤレス通信、

テラビット ワイヤード通信、先進運転支援システム (ADAS)、産業用 IoTなどの次世代アプリケーションに対応

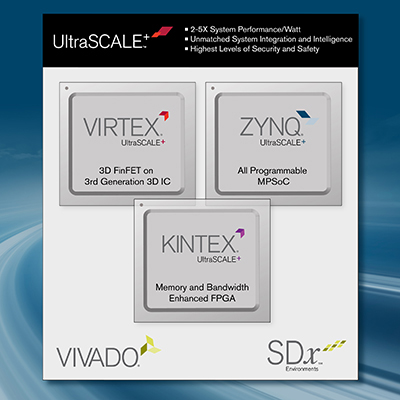

ザイリンクス社 (本社:米国カリフォルニア州サンノゼ、NASDAQ:XLNX) は 2015年2月23日 (米国時間)、最新のメモリ テクノロジ、3D-on-3Dテクノロジおよびマルチプロセッシング システム オン チップ (MPSoC) テクノロジを組み合わせた、一世代先の価値を提供する16nm UltraScale+™ファミリを発表した。UltraScale+ ファミリは、FPGA、3D ICおよびMPSoCで構成されており、パフォーマンスと集積度をさらに向上するため、新しいインターコネクト最適化テクノロジであるSmartConnectも搭載されている。UltraScale+ ファミリにより、ザイリンクスのUltraScaleポートフォリオは、20nmから16nmのFPGA、SoCおよび3D ICデバイスに拡充された。UltraScale+ ファミリは、TSMC社製 16FF+ FinFET 3Dトランジスタの1ワット当たりの性能の劇的な向上を活用したものである。システム レベルで最適化されたUltraScale+は、従来のプロセス ノード移行をはるかにしのぐ価値を提供する。28nmデバイスと比較して、システム レベルでの1ワット当たりの性能は2~5倍となり、システム集積度とインテリジェンスが大きく向上するとともに、最高のセキュリティ性能と安全性も実現された。

今回拡充されるザイリンクスUltraScale+ FPGAポートフォリオは、Kintex® UltraScale+ FPGA、Virtex® UltraScale+ FPGAおよび3D ICファミリで構成されており、Zynq® UltraScale+ ファミリには、業界初のAll Programmable MPSoCが含まれる。このポートフォリオによって、LTE Advanced、5Gワイヤレス通信、テラビットワイヤード通信、先進運転支援システム(ADAS)、産業用 IoT(モノのインターネット)など、幅広い次世代アプリケーションに対応する。

メモリが強化されたプログラマブル デバイス : UltraRAMは、大容量のSRAMをデバイス内に集積することで、FPGAおよびSoCベースのシステム性能と消費電力における最大のボトルネックの一つを解決する。この新しい大容量メモリを使用することで、ディープ パケットやビデオ バッファリングなどの用途に対して大容量のオンチップ メモリを作成でき、低レイテンシ化とパフォーマンスの向上が可能になる。大容量のメモリを処理エンジンの極めて近くに実装することで、1ワット当たりのシステム性能を向上させ、BOMコストを削減できる。UltraRAMは、さまざまなコンフィギュレーションが可能で、最大432Mbitまで対応する。

SmartConnectテクノロジ : SmartConnectは、FPGA向けの革新的で新しいインターコネクト最適化テクノロジである。システム全体のインテリジェントなインターコネクト最適化を行うことで、パフォーマンス、面積、消費電力性能をさらに20~30%向上させる。UltraScaleアーキテクチャが配線、クロッキング、ロジック ファブリックを再設計することによってシリコン レベルでインターコネクト ボトルネックに対処するのに対し、SmartConnectは、デザイン固有のスループットおよびレイテンシ要件に合ったインターコネクト トポロジの最適化を行い、インターコネクト ロジックの面積を削減する。

業界初の3D-on-3Dテクノロジ : UltraScale+ポートフォリオのハイエンド製品では、3Dトランジスタと第3世代のザイリンクス3D ICの利点を組み合わせて提供する。FinFETによって、プレーナ型トランジスタと比較して1ワット当たりの性能が飛躍的に向上するのと共に、3D ICでも、モノリシック デバイスと比較して1ワット当たりのシステム集積度と帯域幅が飛躍的に向上する。

ヘテロジニアスなマルチプロセッシング テクノロジ : 新しいZynq UltraScale+ MPSoCには、上記のすべてのFPGAテクノロジとともに、これまでにないレベルのヘテロジニアスなマルチプロセッシングを搭載し、「タスクごとに最適なエンジン」を選択できる。これにより、従来の製品と比較して、1ワット当たりのシステム性能を5倍向上する。プロセッシング サブシステムの中核となっているのは、ハードウェア仮想化、非対称プロセッシングに対応し、ARM® TrustZone®を完全サポートする64ビット クアッド コアARM Cortex®-A53プロセッサである。

プロセッシング サブシステムには、リアルタイム性が要求される用途向けにデュアル コアARM Cortex-R5リアルタイム プロセッサも搭載されており、即応性、高スループット、低レイテンシを提供すると共に、最高レベルの安全性および信頼性を実現する。独立したセキュリティ ユニットは、マシン間(M2M)通信や産業用IoTアプリケーションで標準的に要求される、セキュア ブート、キー&ヴォールト管理、改ざん防止性能といった軍用レベルのセキュリティ ソリューションを実現する。

グラフィックス アクセラレーションとビデオ圧縮/解凍用途には、専用のグラフィック プロセッサであるARM Mali™-400MPおよびH.265ビデオ コーデック ユニットを搭載しており、入出力インターフェースとしてDisplayPort、MIPIおよびHDMIもサポートする。加えて、各プロセッシング エンジンのシステム モニタリング、システム管理およびダイナミック パワー ゲーティングを支援する専用のプラットフォームおよびパワー マネージメント ユニット(PMU)も用意されている。

ザイリンクスのプログラマブル製品グループ担当エグゼクティブ バイス プレジデント兼ジェネラル マネージャのヴィクター ペン(Victor Peng)は、「ザイリンクスは、16nm FinFET FPGAおよびMPSoCによって、さまざまな次世代のアプリケーションに一世代先の価値を提供します。ザイリンクスの新しいUltraScale+ 16nmポートフォリオは、システムレベルで2~5倍の1ワット当たり性能の向上、そして、システム集積度とインテリジェンスの劇的な向上や最高レベルのセキュリティ性能と安全性の提供などで、お客様のニーズに応えます。これらの価値により、ザイリンクスは市場を大きく拡大することができます」と述べている。

TSMC社のビジネス開発担当バイス プレジデントのB J ウー(B J Woo)博士は、「現在継続中のザイリンクスとTSMCによる業務提携により、世界トップクラスの16nm FinFETプロセスによる製品を実現しました。ザイリンクスとTSMCは、最低の消費電力で最高のシステム価値をもたらす最先端のシリコンパフォーマンスを実証しました」と述べている。

供給体制

UltraScale+ファミリの全ての製品で、顧客向けアーリー アクセス プログラムを実施中である。最初のテープ アウトとデザイン ツールのアーリー アクセス プログラムは、2015年第2四半期に予定されている。また、最初の出荷は、2015年第4四半期に予定されている。最新のZynq UltraScale+ MPSoCテクノロジのデモについては、2月24日~26日にドイツのニュルンベルクで開催されるEmbedded World 2015のザイリンクス ブース(スタンド 1-205)で展示する。詳しい情報は、http://japan.xilinx.com/ultrascale で公開している。

ザイリンクスについて

ザイリンクスは、All Programmable FPGAおよびSoC、3D ICの世界的なリーディング プロバイダーである。業界をリードするこれらデバイスを次世代設計環境およびIPとともに提供することで、プログラマブル ロジックからプログラマブル システム インテグレーションまで、幅広いユーザー ニーズに応える。詳しい情報は、ウェブサイト japan.xilinx.com で公開している。

※ ザイリンクスの名称およびロゴ、Artix、ISE、Kintex、Spartan、Virtex、Vivado、Zynq、その他本プレスリリースに記載のブランド名は米国およびその他各国のザイリンクスの登録商標または商標です。ARMは EUおよびその他の国での ARMの登録商標および商標です。その他すべての名称は、それぞれの所有者に帰属します。

ザイリンクス株式会社ホームページはこちら